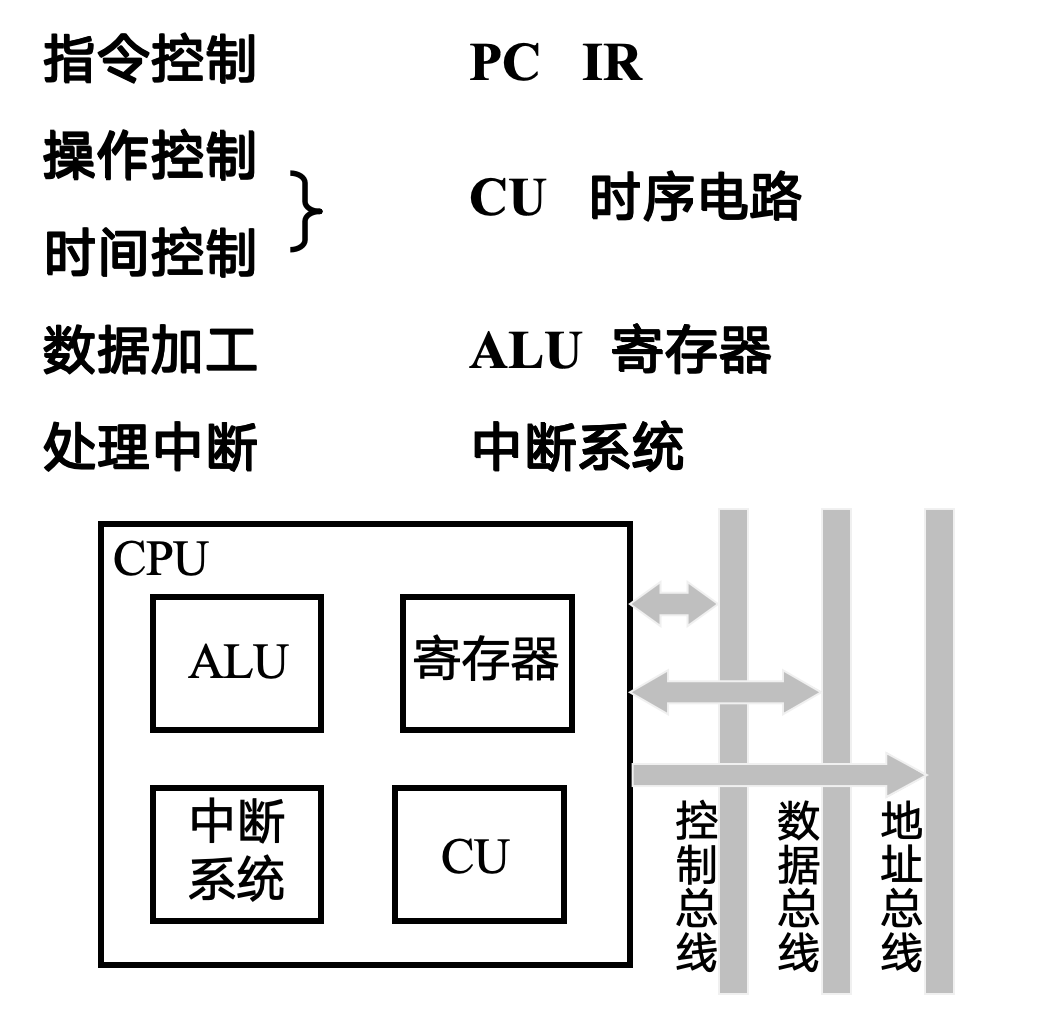

CPU的结构和功能

CPU的结构

CPU的功能

- 控制器的功能

- 取指令

- 分析指令

- 执行指令,发出各种操作命令

- 控制程序输入以及结果输出

- 总线管理

- 处理异常情况

- 运算器的功能

- 算数运算

- 逻辑运算

CPU结构框图

CPU与系统总线

CPU的内部结构

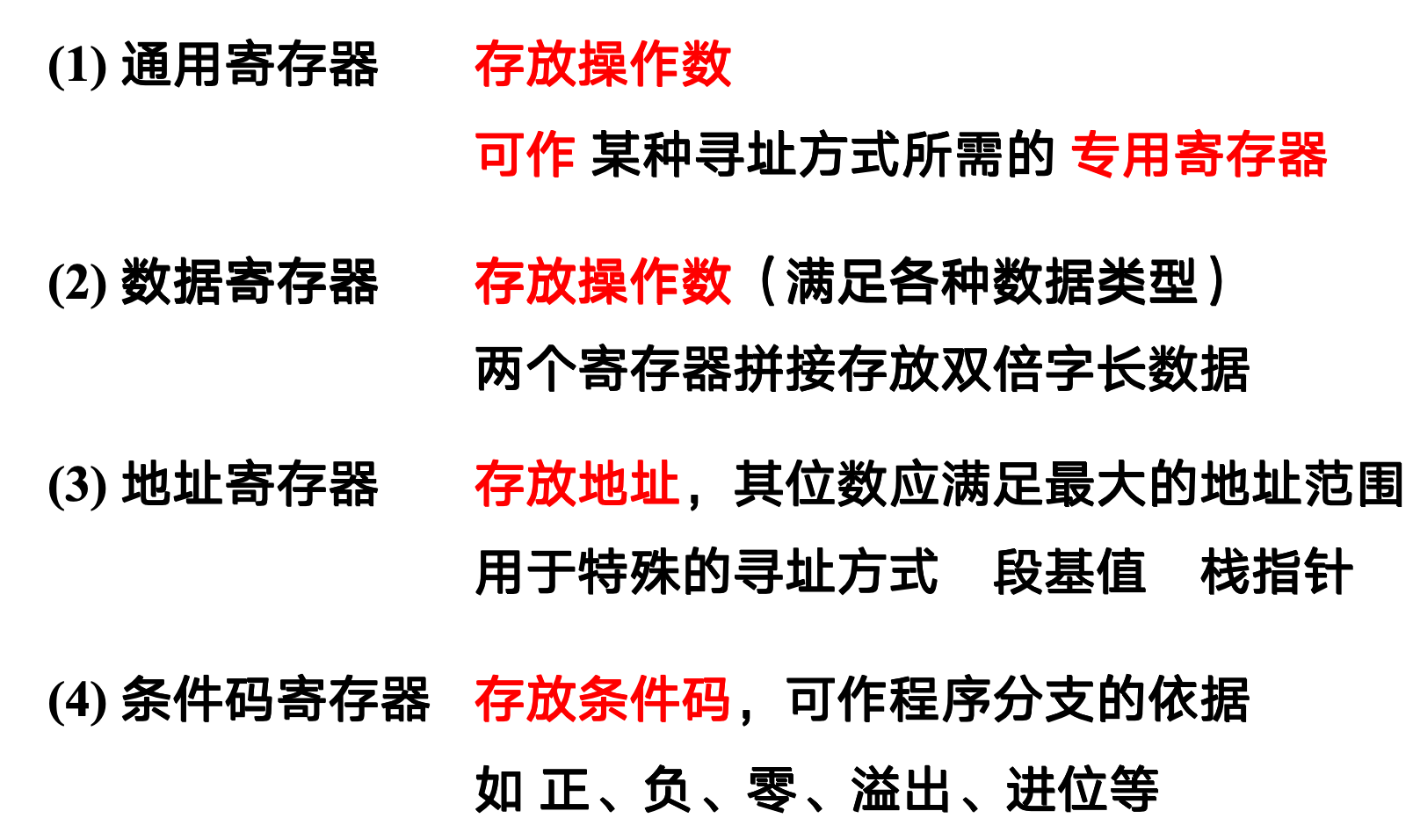

CPU的寄存器

用户可见寄存器

控制和状态寄存器

控制寄存器

$PC \rightarrow M\rightarrow M\rightarrow MDR \rightarrow IR$

MAR MDR IR用户不可见

PC用户可见 一般也不修改

状态寄存器

状态寄存器存放的是条件码

PSW寄存器存放的时候程序状态字

控制单元CU和中断系统

CU产生全部指令的微操作命令序列

中断系统…

ALU

第六章

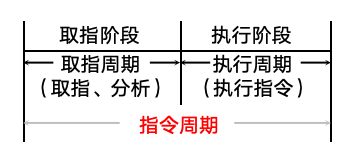

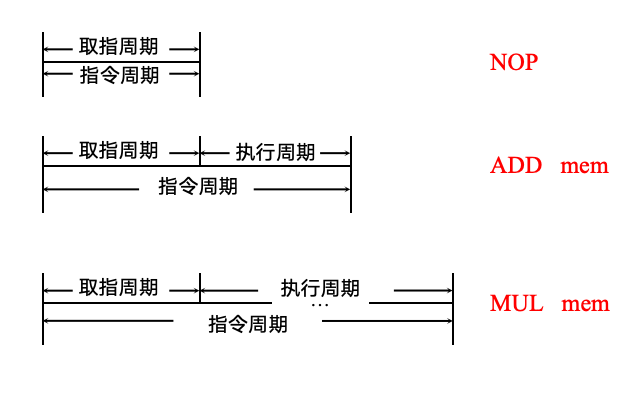

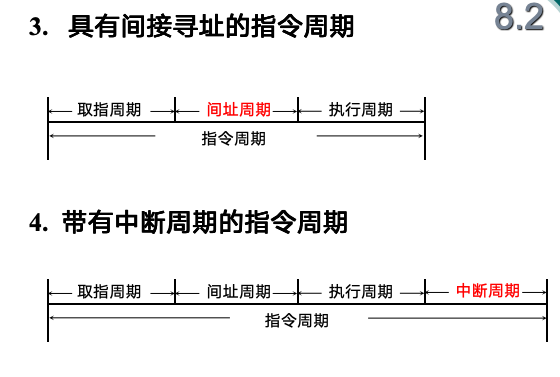

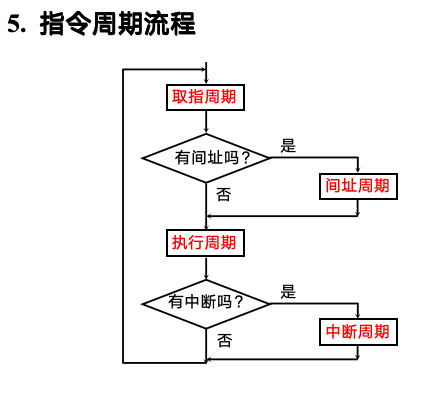

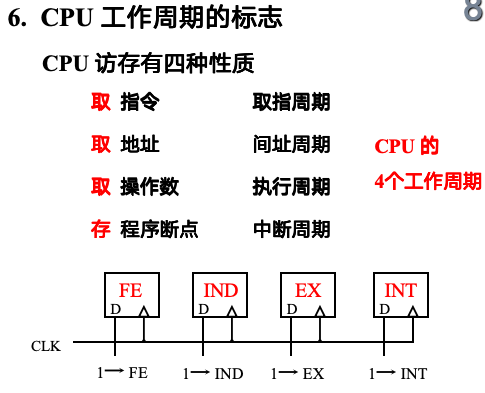

指令周期

取出并执行一条指令所需的全部时间

每条指令的周期是不同的

指令流水

在提高硬件速度之外的基础上

提高整机处理能力 ,改进系统结构,开发系统的并行性

并行是指:并发和同时

并发指两个或以上事件在同一时间段发送

同时指两个或以上事件在同一时刻发生

并行性的等级

过程级 粗粒度 软件实现

指令级 细粒度 硬件实现

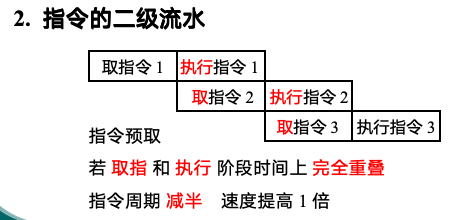

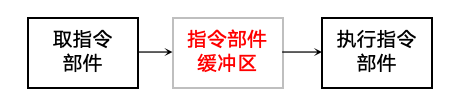

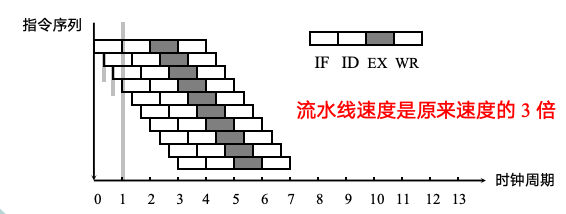

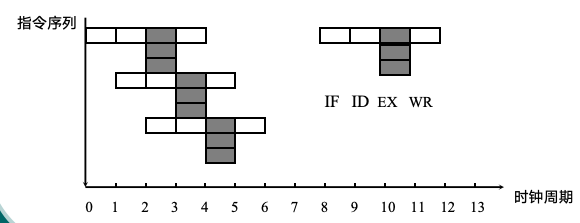

指令流水很容易理解,如果是串行执行,那么取指令和执行指令的过程总有一个部件是空闲的

事实上完全可以在取指令后,执行指令的阶段,同时读取第二个指令,这样子做就是指令的二级流水

若取指和执行在阶段时间上完全重叠,那么指令周期减半,速度提高一倍

影响指令流水效率加倍的因素

执行时间>取指时间

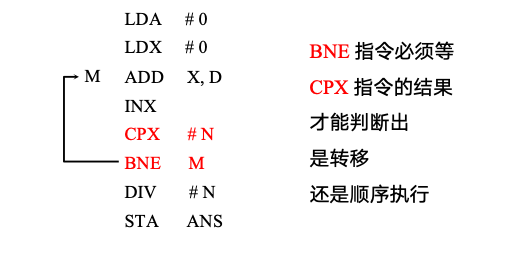

条件转移指令对指令流水的影响

必须等上调指令结束,才能确定下条指令的地址

这样造成的时间损失 可以用猜测法弥补

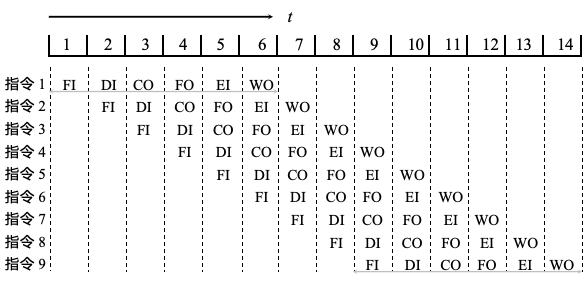

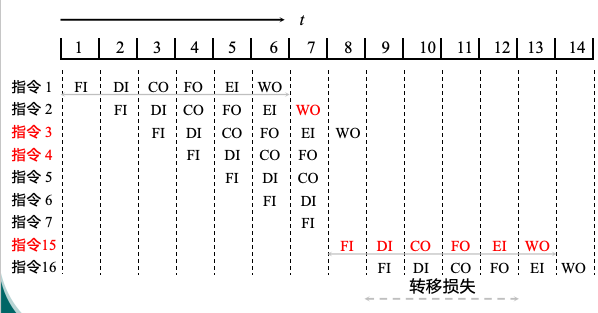

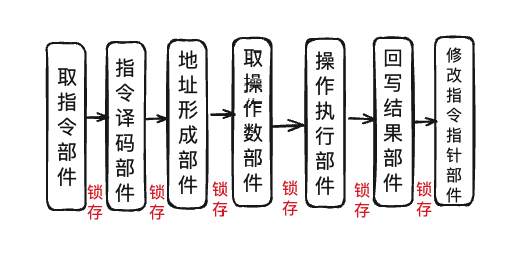

指令的六级流水

完成一条指令需要六个时间单位,需要执行9次

若串行执行,则需要54个时间单位

若采用六级流水,则只需要14个时间单位

影响指令流水线性能的因素

程序相近指令之间出现某种关联,使得指令流水出现停顿,影响流水线效率

若结构相关 即不同指令争用同一功能部件产生资源冲突 解决办法是停顿、指令存储器和数据存储器分开、指令预取技术

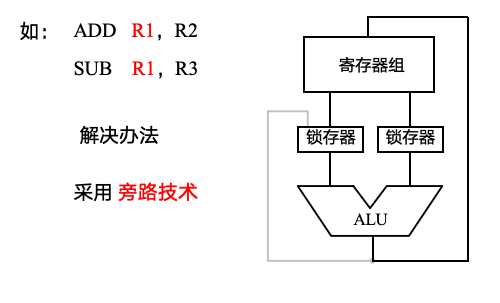

数据相关的

比如两条指令都需要用同一个数据

或者用后推法

控制相关的由转移指令引起的

流水线的性能

吞吐率

单位时间内流水线所完成指令或输出结果的数量 设m段流水线各段时间为$\Delta t$

- 最大吞吐率 $T_{pmax}= \frac{1}{\Delta t}$

- 实际吞吐率 连续处理n条指令的吞吐率为$T_p=\frac{n}{m \cdot \Delta t+ (n-1) \cdot \Delta t}$

加速比 $S_p$

m段的流水线的速度与等功能的非流水线的速度之比,设各段流水线为$\Delta t$

完成n条指令在m段流水线上共需 $T=m \cdot \Delta t + (n-1) \cdot \Delta t$

完成n条指令在等效的非流水线上共需

$T^{‘}=nm \cdot \Delta t$

则$S_p = \frac{nm \cdot \Delta t}{m \Delta t + (n-1) \cdot \Delta t }=\frac{nm}{m+n-1} $

超流水线技术

在一个时钟周期内再分段

在一个时钟周期内一个功能部件使用多次

不能调整指令的执行顺序

靠编译程序优化

超长指令字技术

由编译程序挖掘出指令间潜在的并行性,将多条能并行操作的指令组合成一条,具有多个操作码字段的超长指令字

采用多个处理部件

流水线结构

完成一条指令分为七段,每段一个时钟周期

若流水线不出现断流 一个时钟周期出一个结果

不采用流水技术 七个时钟周期出一个结果

理想情况下面速度是7倍

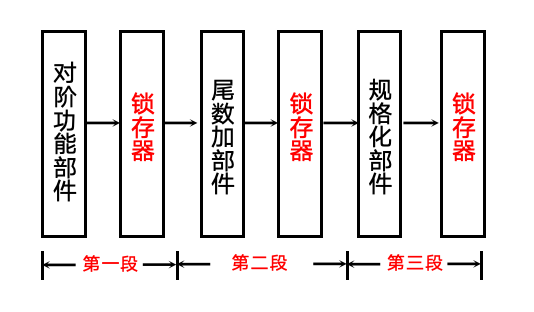

运算流水线

完成浮点运算加减可分:

对阶、尾数求和、规格化三段

分段原则是让每段操作时间尽量一致